- 您现在的位置:买卖IC网 > Sheet目录3882 > PIC16F87T-E/ML (Microchip Technology)IC MCU FLASH 4KX14 EEPROM 28QFN

108

8008H–AVR–04/11

ATtiny48/88

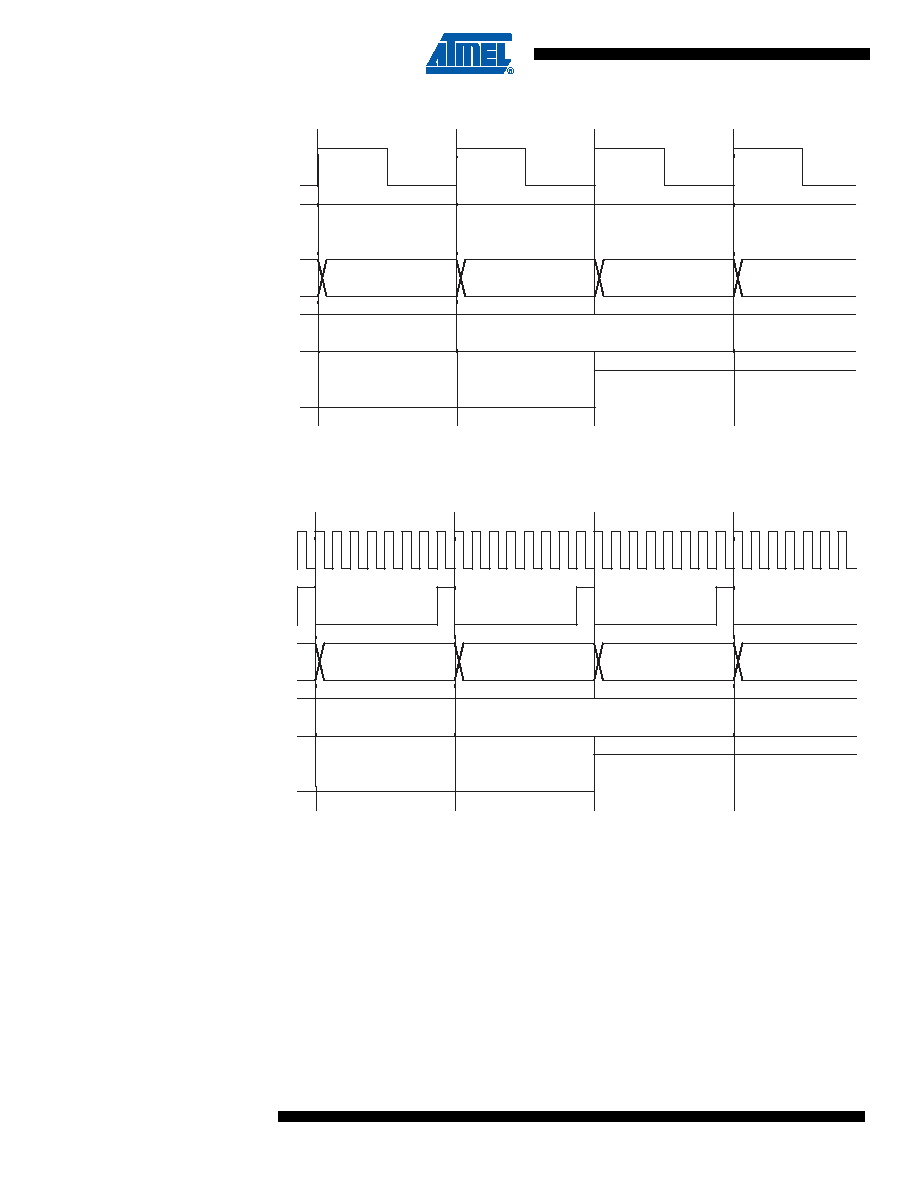

Figure 12-10. Timer/Counter Timing Diagram, Setting of OCF1x, no Prescaling

Figure 12-11 shows the same timing data, but with the prescaler enabled.

Figure 12-11. Timer/Counter Timing Diagram, Setting of OCF1x, with Prescaler (f

clk_I/O/8)

Figure 12-12 shows the count sequence close to TOP in various modes. When using phase and

frequency correct PWM mode the OCR1x Register is updated at BOTTOM. The timing diagrams

will be the same, but TOP should be replaced by BOTTOM, TOP-1 by BOTTOM+1 and so on.

The same renaming applies for modes that set the TOV1 Flag at BOTTOM.

clk

Tn

(clk

I/O/1)

OCFnx

clk

I/O

OCRnx

TCNTn

OCRnx Value

OCRnx - 1

OCRnx

OCRnx + 1

OCRnx + 2

OCFnx

OCRnx

TCNTn

OCRnx Value

OCRnx - 1

OCRnx

OCRnx + 1

OCRnx + 2

clk

I/O

clk

Tn

(clk

I/O/8)

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC16F87-E/ML

IC MCU FLASH 4KX14 EEPROM 28QFN

PIC18LF4320-I/ML

IC MCU FLASH 4KX16 EEPROM 44QFN

PIC16F77T-I/PTG

IC MCU FLASH 8KX14 W/AD 44TQFP

PIC16LF1933-I/SO

IC PIC MCU FLASH 4K 28-SOIC

PIC16C54C-20I/SO

IC MCU OTP 512X12 18SOIC

PIC16LF726-I/SO

IC PIC MCU FLASH 8K 1.8V 28-SOIC

PIC12CE673-10/P

IC MCU OTP 1KX14 A/D&EE 8DIP

PIC16F726-I/SO

IC PIC MCU FLASH 8KX14 28-SOIC

相关代理商/技术参数

PIC16F87T-E/SO

功能描述:8位微控制器 -MCU 20MHz 4K Flash RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F87T-E/SS

功能描述:8位微控制器 -MCU 20MHz 4K Flash RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F87T-I/ML

功能描述:8位微控制器 -MCU 7KB 368 RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F87T-I/SO

功能描述:8位微控制器 -MCU 7KB 368 RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F87T-I/SS

功能描述:8位微控制器 -MCU 7KB 368 RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F882-E/ML

功能描述:8位微控制器 -MCU 3.5KB Enh FLSH 128 RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F882-E/SO

功能描述:8位微控制器 -MCU 3.5KB Enh FLSH 128 RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F882-E/SP

功能描述:8位微控制器 -MCU 3.5KB Enh FLSH 128 RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT